DRAM <Merkmale von Halbleiterspeichern>

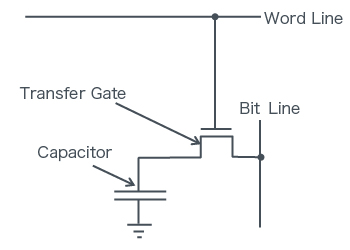

Speicherzellenstruktur

Besteht aus einem Transistor und einem Kondensator

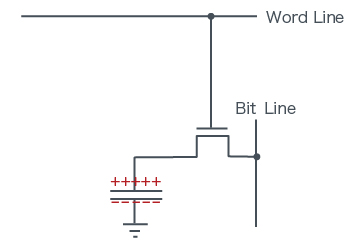

Datenschreibmethode

[Bei „1"]

- Potenzial der Wortleitung ist hoch

- Potenzial der Bitleitung ist hoch

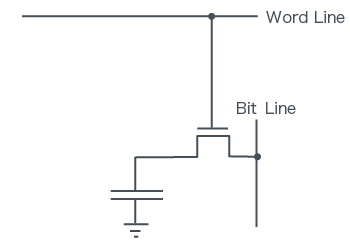

- Potenzial der Wortleitung ist niedrig

Der Zustand „1"

Der Zustand „0"