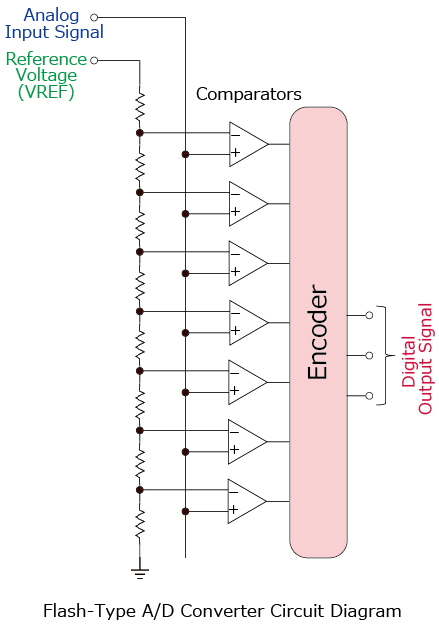

A/D-Wandler Grundkonfiguration 1 (Flash-Methode)

Diese Art von ADC verwendet 2N-1-Vergleicher (für einen N-Bit-Wandler), um das analoge Signal mit aufeinanderfolgenden Referenzspannungen zu vergleichen. Die Ergebnisse werden dann mithilfe eines Encoders in ein digitales Format umgewandelt.

Funktionen

- Analoge Signale werden direkt in digitale Signale umgewandelt (da die Vergleicher selbst die Sampling-Geräte sind), wodurch ein Sample-and-Hold-Schaltkreis überflüssig wird.

- Somit wird eine extrem schnelle Umwandlung ermöglicht (Sampling-Frequenzen von über 1 GHz sind möglich).

- Durch die relativ größere Größe und den höheren Stromverbrauch (aufgrund der Anzahl von Vergleichern sind 2N-1 erforderlich) beschränken die Auflösung auf ungefähr 8 Bits.